## COURSE GUIDE

## IFT 212 COMPUTER ARCHITECTURE AND ORGANIZATION

Course Team Greg Onwodi (Developer/Writer) - NOUN

J. B. Awotunde (Reviewer) - Unillorin Prof Joshua Abah (Course Editor)

NATIONAL OPEN UNIVERSITY OF NIGERIA

IFT 212 COURSE GUIDE

©2025 by NOUN Press

National Open University of Nigeria

Headquarters

University Village

Plot 91, Cadastral Zone

Nnamdi Azikiwe Expressway

Jabi, Abuja

Lagos Office 14/16 Ahmadu Bello Way Victoria Island, Lagos

e-mail: centralinfo@nou.edu.ng

URL: www.nou.edu.ng

All rights reserved. No part of this book may be reproduced, in any form or by any means, without exclusive permission in writing from the publisher.

Printed 2009

Reviewed and Reprinted 2025

ISBN:978-978-786-494-4

# MAIN COURSE

| CONTENT                              | CONTENTS                                                            |     |

|--------------------------------------|---------------------------------------------------------------------|-----|

| Module 1                             | Organization And Architecture                                       |     |

| Unit 1                               | Introduction To Computer Architecture And Organization              |     |

| Unit 2                               | Instruction Sets Characteristics                                    |     |

| Module 2                             | Computer Arithmetic                                                 | 20  |

| Unit 1<br>Unit 2                     | The Arithmetic Implementation                                       |     |

| Module 3                             | Cpu Organization                                                    | 54  |

| Unit 1<br>Unit 2<br>Unit 3           | Cpu Organization                                                    | 6   |

| Module 4                             | Instruction Set Architecture                                        | 80  |

| Unit 1<br>Unit 2                     | General Overview Of Instruction Set Architecture. Instruction Cycle |     |

| Module 5                             | The Memory Systems                                                  | 103 |

| Unit 1<br>Unit 2<br>Unit 3<br>Unit 4 | Computer Memory  Memory Hierarchy  Virtual Memory  Cache Memory     | 114 |

|                                      |                                                                     |     |

## MODULE 1 ORGANIZATION AND ARCHITECTURE

Unit 1 Introduction to Computer Architecture

and Organization

Unit 2 Instruction Sets Characteristics

and Functions

Unit 3 Types of Operands

# UNIT 1 INTRODUCTION TO COMPUTER ARCHITECTURE AND ORGANIZATION

#### **CONTENTS**

- 1.0 Introduction

- 2.0 Objectives

- 3.0 Main Content

- 3.1 Computer Organization and Architecture

- 3.2 Structure and Function

- 3.3 Computer Components

- 3.4 Instruction Fetch and Execute

- 4.0 Conclusion

- 5.0 Summary

- 6.0 Tutor-Marked Assignment

## 1.0 INTRODUCTION

Despite the variety and pace of change in the computer field, certain fundamental concepts consistently apply throughout. The application of these concepts depends on the current state of technology and the price/performance objectives of the designer.

Many computer manufacturers offer a family of computer models, all with the same architecture but with differences in their organization. In a class of computers called microcomputers, the relationship between architecture and organization is very close. Changes in technology not only influence organizations but also result in the introduction of more powerful and complex architectures. However, because a computer organization must be designed to implement a particular architectural specification, a thorough treatment of organization requires a detailed examination of the architecture as well.

#### 2.0 OBJECTIVES

At the end of this unit, you should be able to:

- Explain the operational units of a computer system.

- Outline types of operands and operations specific by machine instruction.

- Explain opcodes, operands, and addressing modes

#### 3.0 MAIN CONTENT

## 3.1 COMPUTER ORGANIZATION AND ARCHITECTURE

Although it is difficult to give a precise definition, a consensus exists about the general area covered by it. Computer organization refers to the operational units and their interconnection that realize the architectural specification.

Examples of architectural attributes include the instruction set, the number of bits used to represent various data types (e. g numbers, characters), I/O mechanism, and techniques for addressing memory. Organizational attributes include hardware details transparent to the programmer, such as control signals; interfaces between the computer peripherals, and memory technology used.

In computer engineering, computer architecture is a set of rules and methods that describe the functionality, organization, and implementation of computer systems. The architecture of a system refers to its structure in terms of separately specified components of that system and their interrelationships.

Computer architecture consists of rules and methods or procedures that describe the implementation, and functionality of the computer systems. We can define computer architecture based on its performance, efficiency, reliability, and cost of the computer system. It deals with software and hardware technology standards.

## 3.2 STRUCTURE AND FUNCTION

A computer is a computer system, contemporary computers contain millions of elementary electronic components.

- **Structure:** How the components are interrelated.

- **Function:** The operation of each component as part of the structure.

In terms of description, there are two choices: starting at the bottom and building up to a complete description, or beginning with a top view and decomposing the system into its subparts. Evidence from several fields suggests that the top-down approach is the clearest and most effective.

The approach taken is that the computer be described from the top down.

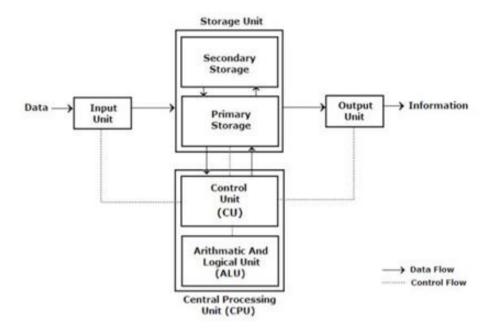

Both the structure and functioning of a computer are simple. Figure 1 depicts the basic functions that a computer can perform. In general terms, there are only four:

- Data processing

- Data storage

- Data movement

- Control

**Figure 1:** The Basic Functions of Computer

The computer, of course, must be able to process data. The data may take a wide variety of forms, and the range of processing requirements ID broad. It is also essential that a computer stores data. Even if the computer is processing data on the fly (i.e. data come in and get processed and the results go out immediately) the computer must temporarily store at least. Those pieces of data that are being worked on at any given moment. Files of data are stored on the computer for subsequent retrieval and update.

The computer must be able to move data between itself and the outside world. The computer's operating environment consists of devices that serve as either sources or destinations of data. When data are received from or delivered to a device that is directly connected to the computer, the process is known as input-output (I/O), and the device is referred to as a peripheral. When data are moved over longer distances, to or from a remote device, the process is known as data communications. Finally, there must be control of these three functions. Ultimately, this control is exercised by the individuals who provide the computer with instructions. Within the computer, a control unit manages the resources of the computer and orchestrates the performance of its functional parts in response to those instructions.

There are four main structural components

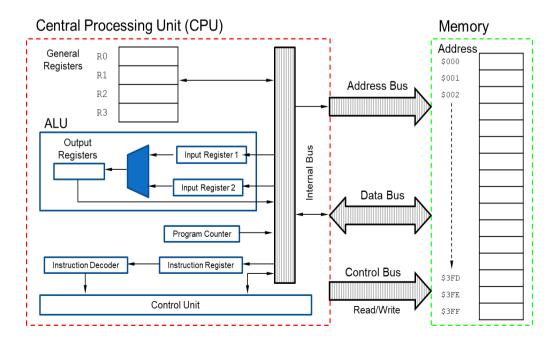

- **The central processing unit (CPU)**: Controls the operations of the computer and performs its data processing functions; often simply referred to as a processor.

- Main memory: Stores data

- **I/O:** Moves data between the computer and its external environment.

- **System interconnections**: Some mechanism that provides for communication among CPU, main memory, and I/O. A common example of system interconnection is through a system bus, consisting of several conducting wires to which all the other components attach.

However, the most interesting and complex component is the CPU. Its major structural components are as follows:

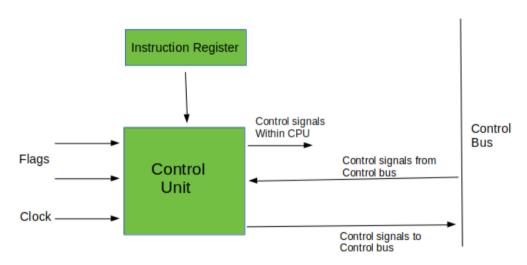

- **Control unit**: Controls the operations of the CPU and hence the computer.

- **Arithmetic and logic unit (ALU)**: Performs the computer data processing functions.

- Registers: Provides storage internal to the CPU.

- **CPU interconnection**: Some mechanism that provides for communication among the control unit, ALU, and registers.

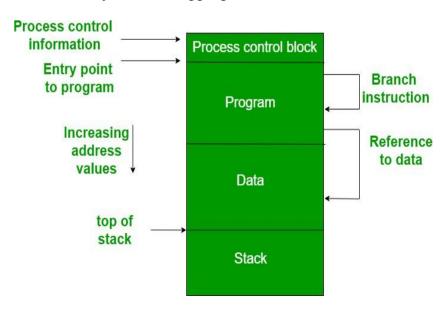

## 3.3 COMPUTER COMPONENTS

Virtually all contemporary computer designs are based on concepts developed by John Von Neumann at the Institute for Advanced Studies Princeton. Such a design is referred to as the *Von Neumann architecture* and is based on three key concepts:

- Data and instructions are stored in a single read-write memory.

- The contents of this memory are addressable by location, without regard to the type of data contained there.

- Execution occurs sequentially (unless explicitly modified) from one instruction to the next.

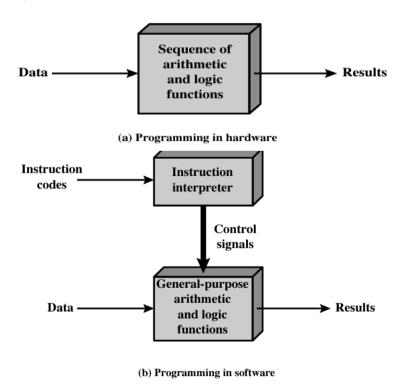

There is a small set of basic logic components that can be combined in various ways to store binary data and to perform arithmetic and logical operations on that data. If there is a particular computation to be performed, a configuration of logic components designed specifically for that computation could be constructed. We can think of the process of connecting the various components in the desired configuration as a form of programming. The resulting "program" is in the form of hardware and is termed a *hardwired program*.

Now consider this alternative. Suppose we construct a general-purpose configuration of arithmetic and logic functions. This set of hardware will perform various functions on data depending on control signals applied to the hardware. In the original case of customized hardware, the system accepts data and produces results Figure 2a. With general-purpose hardware, the system accepts data and control signals and produces results. Thus, instead of rewiring the hardware for each new program, the programmer merely needs to supply a new set of control signals.

How shall control signals be supplied? The answer is simple but subtle. The entire program is a sequence of steps. At each step, some arithmetic or logical operation is performed on some data. For each step, a new set of control signals is needed. Let us provide a unique code for each possible set of control signals, and let us add to the general-purpose hardware a segment that can accept a code and generate control signals (Figure 2b).

Figure 2. Hardware and Software Approaches

Programming is now much easier. Instead of rewiring the hardware for each new program, all we need to do is provide a new sequence of codes. Each code is, in effect, an instruction, and part of the hardware interprets each instruction and generates control signals. To distinguish this new method of programming, a sequence of codes or instructions is called *software*.

Figure 2b indicates two major components of the system: an instruction interpreter and a module of general-purpose arithmetic and logic functions. These two constitute the CPU. Several other components are needed to yield a functioning computer. Data and instructions must be put into the system. For this, we need some sort of input module. This module contains basic components for accepting data and instructions in some form and converting them into an internal form of signals usable by the system. A means of reporting results is needed, and this is in the form of an output module. Taken together, these are referred to as I10 *components*.

One more component is needed. An input device will bring instructions and data in sequentially. But a program is not invariably executed sequentially; it ma, jump around (e.g., the IAS jump instruction). Similarly, operations on data may require access to more than just one element at a time in a predetermined sequence Thus, there must be a place to store temporarily both instructions and data. That module is called *memory*, or *main memory* to distinguish it from external storage of peripheral devices. Von Neumann pointed out that the same memory could be used to store both instructions and data.

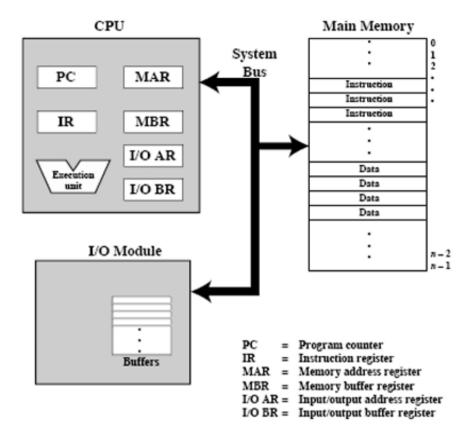

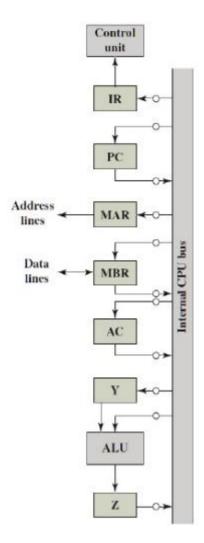

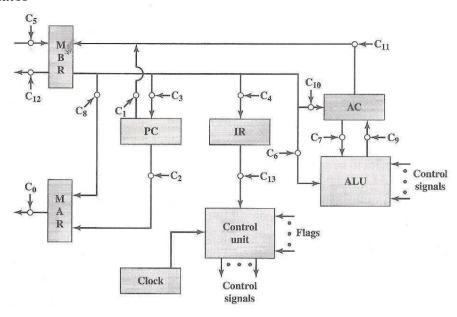

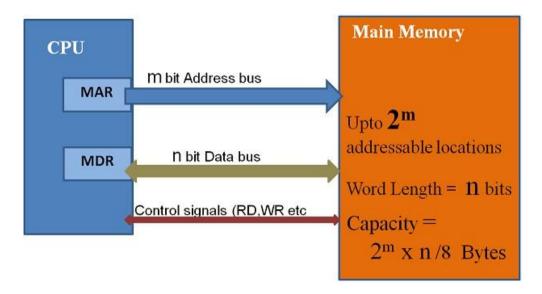

Figure 3 illustrates these top-level components and suggests the interaction among them. The CPU exchanges data with memory. For this purpose, it typically makes use of two internal (to the CPU) registers: a memory address register (MAR), which specifies the address in memory for the next read or write, and a memory buffer register (MBR), which contains the data to be written into memory receives the data read from memory. Similarly, an I/0 address register (I/OAR specifies a particular 1/0 device. An I/0 buffer (I/OBR) register is used for the exchange of data between an I/0 module and the CPU.

A memory module consists of a set of locations, defined by sequentially numbered addresses. Each location contains a binary number that can be interpreted as either an instruction or data. A 1/0 module transfers data from external devices' CPU and memory, and vice versa. It contains internal buffers for temporarily holding these data until they can be sent on.

Having looked briefly at these major components, we now turn to an overview of how these components function together to execute programs.

Figure 3. Computer Components Top-level View

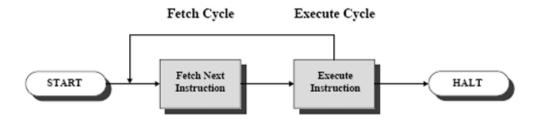

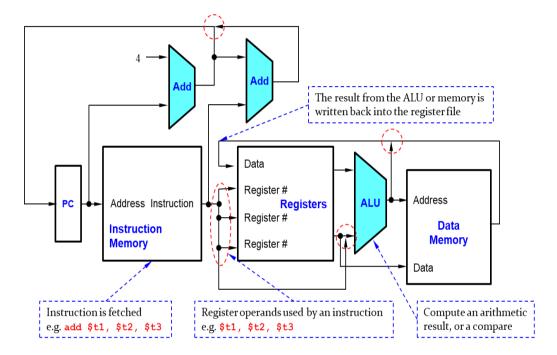

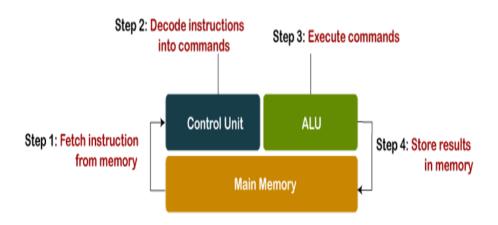

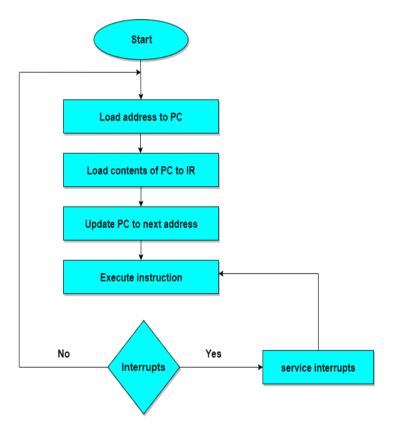

The key elements of program execution. In its simplest form, instruction processing consists of two steps: The processor reads (fetches) instructions from memory one at a time and executes each instruction. Program execution consists of repeating the process of instruction fetch and instruction execution. The instruction execution may involve several operations and depends on the nature of the instruction (see, for example, the lower portion of Figure 2.4).

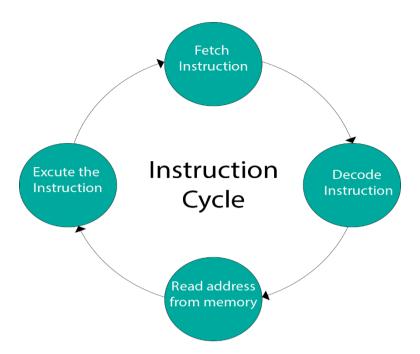

The processing required for a single instruction is called an *instruction* cycle.

The two steps are referred to as the *fetch cycle* and the *execute cycle*. Program execution halts only if the machine is turned off, some sort of unrecoverable error occurs, or a program instruction that halts the computer is encountered.

## 3.4 Instruction Fetch and Execute

At the beginning of each instruction cycle, the processor fetches an instruction from memory. In a typical processor, a register called the program counter (PC) holds the address of the instruction to be fetched next. Unless told otherwise, the processor. Using the simplified two-step description given previously, the instruction cycle is depicted in Figure 4.

Figure 4. Basic Instruction Cycle

Explain an instruction fetch using the components of Figure 3

- 1) The PC holds the address of the next instruction to execute. The contents of the PC are placed on the System Bus and the PC is incremented to the next instruction to be executed.

- 2) The instruction from Main Memory is retrieved and placed into the IR using the System Bus.

**Note:** The MAR and MBR registers are also used in the process but for now we will ignore their use for simplicities sake.

The processor will then interpret the instruction and perform an action. What are these possible actions? always increments the PC after each instruction fetch so that it will fetch the next instruction in sequence (i.e., the instruction located at the next higher memory address). So, for example, consider a computer in which each instruction occupies one 16-bit word of memory. Assume that the program counter is set to location 300. The processor will next fetch the instruction at location 300. On succeeding instruction cycles, it will fetch instructions from locations 301, 302, 303, and so on. This sequence may be altered, as explained presently.

The fetched instruction is loaded into a register in the processor known as the instruction register (IR). The instruction contains bits that specify the action the processor is to take. The processor interprets the instruction and performs the required action. In general, these actions fall into four categories:

- i. Processor-memory: Data may be transferred from processor to memory or from memory to processor.

- ii. Processor-I/O: Data may be transferred to or from a peripheral

- device be transferring between the processor and an I/O module.

- iii. **Data processing:** The processor may perform some arithmetic or logic operation on data.

- iv. **Control:** An instruction may specify that the sequence of execution is altered. For example, the processor may fetch an instruction from location 149, which specifies that the next instruction is from location 182. The processor will remember this fact by setting the program counter to 182. Thus, on the next fetch cycle, the instruction will be fetched from location 182 rather than 150.

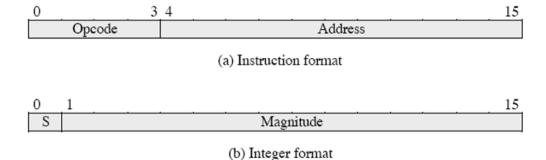

An instruction's execution may involve a combination of these actions. The processor contains a single data register called an accumulator (AC). Both instructions and data are 16 bits long. Thus, it is convenient to organize memory using 16-bit words. The instruction format provides 4 bits for the opcode so that there can be as many as  $2^4 = 16$  different opcodes, aup to 212 = 4096 (4K) words of memory can be directly addressed. Address 941 and stores the result in the latter location. Three instructions, which be described as three fetch and three execute cycles, are required:

- 1. The PC contains 300, the address of the first instruction. This instruction value is 1940 in hexadecimal) is loaded into the instruction register IR anPC is incremented. Note that this process involves the use of a memory dress register (MAR) and a memory buffer register (MBR). For simply these intermediate registers are ignored.

- 2. The first 4 bits (first hexadecimal digit) in the IR indicate that the AC is loaded. The remaining 12 bits (three hexadecimal digits) specify the ac (940) from which data are to be loaded.

- 3. The next instruction (5941) is fetched from location 301 and incremented.

- 4. The old contents of the AC and the contents of location 941 are added an result is stored in the AC.

- 5. The next instruction (2941) is fetched from location 302 and the F is incremented.

- 6. The contents of the AC are stored in location 941.

In this example, three instruction cycles, each consisting of a fetch cycle execute cycle, are needed to add the contents of location 940 to the contents C With a more complex set of instructions, fewer cycles would be needed. Some processors, for example, included instructions that contain more than one address. Thus the execution cycle for a particular instruction on such prop could involve more than one reference to memory. Also, instead of memory references, an instruction may specify an I/O operation. Figure 5 shows the characteristics of a hypothetical machine.

Figure 5. Characteristics of Hypothetical Machine

Program Counter (PC) = Address of Instruction Instruction Register (IR) = Instruction begin executed Accumulator (AC) = Temporary storage

## (c) Internal CPU Registers

0001 = Load AC from Memory 0010 = Store AC to Memory 0101 = Add to AC from Memory

## (d) Partial list of opcodes

For example, the PDP-11 processor includes an instruction, expressed physically as ADD B, A, that stores the sum of the contents of memory location B into memory location A. A single instruction cycle with the following steps

- Fetch the ADD instruction.

- Read the contents of memory location A into the processor.

- Read the contents of memory location B into the processor. To contents of A are not lost, the processor must have at least two registers storing memory values, rather than a single accumulator.

- Add the two values

- Write the result from the processor to memory location A.

Thus, the execution cycle for a particular instruction may involve more than one reference to memory. Also, instead of memory references, an instructor specifies an I/O operation.

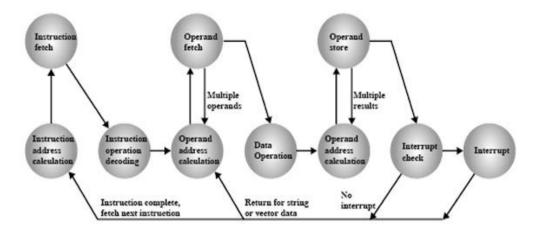

For any given instruction cycle, some states -null and others may be visited more than once. The states can be described as follows:

**Instruction address calculation** (ac): Determine the address of the next instruction to be executed. Usually, this involves adding a fixed number to the address of the previous instruction. For example, if each instruction is 16 bits long and memory is organized into 16-bit words, then add 1 to

the previous ad- dress. If, instead, memory is organized as individually addressable 8-bit bytes, then add 2 to the previous address.

Figure 6. The Instruction Cycle State with Interrupts

Instruction fetch (if): Read instruction from its memory location into the processor.

**Instruction operation decoding (iod):** Analyze instruction to determine the type of operation to be performed and operand(s) to be used.

**Operand address calculation (oac)**: If the operation involves reference to an operand in memory or available via I/O, then determine the address of the operand.

**Operand fetch (of):** Fetch the operand from memory or read it in from 1/O. Data operation (do): Perform the operation indicated in the instruction. Operand store (os): Write the result into memory or out to I/O. States in the upper part of Figure 6 involve an exchange between the processor and either memory or a 1/O module. States in the lower part of the diagram involve only internal processor operations. The oac state appears twice, because an instruction may involve a read, a write, or both. However, the action performed during that state is fundamentally the same in both cases and so only a single state identifier is needed. Also note that the diagram allows for multiple operands and multiple results because some instructions on some machines require this. For example, the PDP-11 instruction ADD A, B results in the following sequence of states: iac, if, iod, oac, of, oac, of, do, oac, os.

Finally, on some machines, a single instruction can specify an operation to be performed on a vector (one-dimensional array) of numbers or a string (one-dimensional array) of characters. As Figure 6 indicates, this would involve repetitive operand fetch and/or store operations.

Table 1. Classes of Interrupts

| Program          | Generated by some conditions that occur as a result of an instruction execution, such as arithmetic overflow, division by zero, attempt to execute an illegal machine instruction, or reference outside a user's allowed memory space. |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Timer            | Generated by a timer within the processor. This allows the operating system to perform certain functions regularly.                                                                                                                    |

| I/O              | Generated by an I/O controller, to signal normal completion of an operation to signal a variety of error conditions.                                                                                                                   |

| Hardware failure | Generated by a failure such as power failure or memory parity error.                                                                                                                                                                   |

#### **Self-Assessment Exercises 1**

Answer the following questions by choosing the most suitable option:

- 1. What is the primary difference between computer organization and computer architecture?

- Organization deals with software while architecture deals A. with hardware

- B. Architecture refers to attributes visible to programmers while organization refers to operational units and their interconnections

- C. Organization is more important than architecture in system design

- There is no difference between the two terms D.

- 2. Which of the following is NOT one of the four basic functions of a computer?

- A. Data processing

- В. Data storage

- C. Data encryption

- D Data movement

- 3. What are the main structural components of a computer system?

- A. CPU, Main memory, I/O, System interconnections

- В. Hardware, Software, Data, Procedures

- C. Input, Processing, Output, Storage

- D. Registers, ALU, Control Unit, Cache

#### **Self-Assessment Exercises 2**

Fill in the gaps in the sentences below with the most suitable words:

1. \_\_\_\_ processing unit (CPU) controls the operations of the computer and performs its data processing functions.

| 2. | The Von Neumann architecture is based on three key concepts, one |

|----|------------------------------------------------------------------|

|    | of which is that data and are stored in a single read-write      |

|    | memory.                                                          |

| 3. | The instruction cycle consists of two main steps: the            |

|    | cycle and the cycle.                                             |

## 4.0 CONCLUSION

Computer architecture and organization form the foundation of modern computing systems. Architecture defines what the system can do - the instruction set, data types, addressing modes, and interface specifications visible to programmers. Organization, on the other hand, determines how these architectural specifications are implemented through hardware components and their interconnections. The Von Neumann architecture remains the dominant model, with its key principles of stored program concept, sequential execution, and unified memory for instructions and data. Understanding the relationship between structure and function, along with the basic computer components (CPU, memory, I/O, and system interconnections), provides the essential knowledge needed to comprehend how modern computers operate and execute instructions.

#### 5.0 SUMMARY

This unit introduced the fundamental concepts of computer architecture and organization. Computer architecture refers to the attributes of a system visible to programmers, including instruction sets, data types, and addressing mechanisms. Computer organization deals with the operational units and their interconnections that realize the architectural specifications. The four basic functions of a computer are data processing, data storage, data movement, and control. A computer system consists of four main structural components: the CPU (which includes the control unit, ALU, and registers), main memory, I/O systems, and system interconnections. The Von Neumann architecture, based on the stored program concept, sequential execution, and unified memory, forms the foundation of modern computer design. The instruction cycle, consisting of fetch and execute phases, describes how computers process individual instructions.

#### 6.0 TUTOR-MARKED ASSIGNMENT

- 1. Explain the distinction between computer architecture and computer organization. Provide two examples of architectural attributes and two examples of organizational attributes. (10 marks)

- 2. Describe the four basic functions of a computer system and explain how these functions interact during program execution. (8 marks)

3. The Von Neumann architecture is fundamental to modern computer design. List and explain the three key concepts on which this architecture is based. Discuss one advantage and one limitation of this architectural approach. (12 marks)

## **Possible Answers to Self-Assessment Exercises**

Self-Assessment Exercise 1

- 1. B

- 2. C

- 3. A

Self-Assessment Exercise 2

- 1. Central

- 2. Instructions

- 3. Fetch, execute

3.2

## UNIT 2 INSTRUCTION SETS CHARACTERISTICS

#### **CONTENTS**

- 1.0 Introduction

- 2.0 Objectives

- 3.0 Main Content

- 3.1 Instruction Formats3.1.1 Instruction Length

- Instruction Sets Characteristics

- 3.2.1 Elements of Machine Instruction

- 3.2.2 Instruction Representation

- 3.3 Instruction Set Design

- 4.0 Conclusion

- 5.0 Summary

- 6.0 Tutor- Marked Assignment

- 7.0 References/ Further Reading

#### 1.0 INTRODUCTION

One boundary where the computer designer and the computer programmer can view the same machine is the machine instruction set. From the designers' point of view, the machine instruction set provides the functional requirements for the processor. Implementing the processor is a task that largely involves implementing the machine instruction set.

#### 2.0 OBJECTIVES

At the end of this unit, you should be able to:

- Explain the instruction format

- Understand the instruction length and characteristics

#### 3.0 MAIN CONTENT

## 3.1 INSTRUCTION FORMATS

An instruction format defines the layout of the bits of an instruction in terms of its constituent fields. An instruction format must include an opcode and implicitly or explicitly, zero or more operands, and The format must implicitly and explicitly, indicate the addressing mode for each operand. For most instruction sets, more than one instruction format is used.

## 3.1.1 INSTRUCTION LENGTH

The most basic design issue to be faced is the instruction format length. These decisions effects and are affected by, memory size, memory organization bus structure process complexity, and processor speed. This decision determines the richness and flexibility of the machine.

## 3.2 INSTRUCTION SETS CHARACTERISTICS

The operation of the processor is determined by the instructions it executes referred to as machine instructions or computer instructions. The collection of different instructions that the processor can execute is referred to as the processor's instruction set.

#### 3.2.1 ELEMENTS OF MACHINE INSTRUCTION

These elements are as follows:

- **Operation code:** Specifies the operation to be performed (e.g., ADD, I/O). The operation is specified by a binary code, known as the operation code or opcode.

- **Source operand reference:** This operation may involve one or more source operands, that is operands that are inputs for the operation

- **Results from operands reference:** The operation may produce a result

- **Next instruction reference:** This tells the processor where to fetch the next instruction after the execution of this instruction is complete.

The address of the next instruction to be fetched could be either a real address or a virtual address, depending on the architecture. Generally, the distinction is transparent to the instruction set architecture. In most cases, the next instruction to be fetched immediately follows the current instruction. In most cases, there is no explicit reference to the next instruction when an explicit reference is needed then the main memory or virtual memory address must be supplied. Source and result operands can be in one of four areas.

- **Main or virtual memory:** As with the next instruction references, the main or virtual memory address must be supplied.

- Processor register: With rare exception, a processor contains one or more registers that may be referenced by machine instructions. If only one register exits reference to it may be implicit. If more than one register exists, then each register is assigned a unique name or number, and the instruction must contain the number of the designed register

- **Immediate:** The value of the operand is contained in a field in the

instruction being executed.

- **I/O device:** The instruction must specify the I/O module and device for operation. If memory-mapped I/O is used, this is just another main or virtual memory address

#### **Self-Assessment Exercises 1**

Answer the following questions by choosing the most suitable option:

- 1. Which of the following is NOT an element of a machine instruction?

- A. Operation code

- B. Source operand reference

- C. Memory address register

- D. Next instruction reference

- 2. What does the opcode specify in an instruction?

- A. The memory location of data

- B. The operation to be performed

- C. The size of the operand

- D. The addressing mode

- 3. How many different opcodes can be represented with 4 bits?

- A. 4

- B. 8

- C. 12

- D. 16

## 3.2.2 INSTRUCTION REPRESENTATION

In a computer, each instruction is represented by a sequence of bits. The instruction is divided into fields corresponding to the constituent elements of the instruction. Opcodes are represented by abbreviations called mnemonics that indicate their operation. Common examples include:

ADD add

SUB SUBTRACT

MUL multiply

DIV divide

LOAD Load data form memory STOR Store data to memory

Operands are also represented in a symbolic manner. For example the instruction ADD, R, Y.

This may mean adding the value contained in data location Y to the contents of register R. In this example, Y refers to the address of a location in memory, and R refers to a particular register. Note that the operation is performed on the contents of a location, not on its address:

Thus, it is possible to write a machine-language program in symbolic form.

X = 413

Y = 414

A simple program accepts this symbolic input, converts opcodes and operand references to binary form, and constructs binary machine instructions. However, symbolic machine language remains a useful tool for describing machine instructions, and we will use it for that purpose.

Assume that variables X and Y correspond to locations 413 and 414, respectively. Assuming a simple set of machine instructions, this operation can be accomplished with three instructions.

- 1. Load a register with the content of memory location 413.

- 2. Add the contents of memory location 414 to the register.

- 3. Store the contents of the register in memory location 413.

## 3.3 INSTRUCTION SET DESIGN

One of the most interesting and most analyzed, aspects of computer design is instruction set is very complex because it affects so many aspects of the computer system. The instruction defines any of the functions performed by the processor and thus has a significant effect on the implementation of the process. The instruction set is the programmer's means of controlling the processor. Thus, programmer requirements must be considered in designing the instruction set. The most important of these fundamental design issues include the following:

- **Operation repertoire:** How many and which operations to provide and how complex operations should be.

- **Data types:** The various types of data upon which operations are performed.

- Instruction format: Instruction length (in nits) number of assesses size of various fields and so on.

- **Registers:** Number of processor registers that can be referenced by instructions and their use.

- **Addressing:** The mode or modes by which the address of an operand is specified.

These issues are highly interrelated and must be considered together in designing an instruction set.

#### 4.0 CONCLUSION

Despite the variety and pace of change in the computer field, certain fundamental concept applies consistently throughout. The application of these concepts depends on the current state of technology and the price/performance objectives of the designer.

#### 5.0 SUMMARY

Computer organization refers to the operational units and their interconnections that realize the architectural specification.

Computer architecture refers to those attributes of a system visible to a programmer or those attributes that have a direct impact on the logical execution of a program. The collection of different instructions that the processor can execute is referred to as the processor's instruction set and an to instruction format defines the layout of the bits of instruction, in terms of its constituents' fields.

#### Possible Answers to Self-Assessment Exercises

Self-Assessment Exercise 1

- 1. C

- 2. B

- 3. D

## 6.0 TUTOR- MARKED ASSIGNMENT

- 1. What in general terms is the distinction between computer organization and computer architecture?

- 2. What are the four main functions of a computer?

- 3. List and briefly explain five important instruction set design issues

## 7.0 REFERENCES/ FURTHER READING

- Hennessy, J. L., & Patterson, D. A. (2011). *Computer architecture: a quantitative approach*. Elsevier.

- Patterson, D. A., Brooks Jr, F. P., Sutherland, I. E., & Thacker, C. P. (2011). *Computer architecture*. Elsevier Science.

- Null, L. (2023). Essentials of Computer Organization and Architecture. Jones & Bartlett Learning.

- Sloss, A; Symes, D; and Wright, C.ARM system developers guide an Fransisco Morgan Kaufmann, 2004

#### MODULE 2 COMPUTER ARITHMETIC

UNIT 1: The Arithmetic Implementation

UNIT 2: Control Flow Design/Implementation

#### UNIT 1 THE ARITHMETIC IMPLEMENTATION

- 1.0 Introduction

- 2.0 Objectives

- 3.0 Main content

- 3.1 The arithmetic and basic unit

- 3.2 Integer representation

- 3.3 Integer Arithmetic

- 3.4 Floating point representation

- 3.5 Floating point arithmetic

- 4.0 Conclusion

- 5.0 Summary

- 6.0 T.M.A

- 7.0 Reference and Further Reading

#### 1.0 INTRODUCTION

This unit focuses on the most complex aspect of the ALU, computer arithmetic. Computer arithmetic is commonly performed on two very different types of numbers: integer and floating point. In both cases, the representation chosen is a crucial design issue and is treated first.

Computer arithmetic is the branch of computer science that deals with the representation and manipulation of numerical quantities in a computer system. Here are some basic concepts and operations involved in computer arithmetic:

- Number systems: Computers use different number systems to represent numerical quantities, including binary (base 2), decimal (base 10), and hexadecimal (base 16) systems. In binary system, each digit can only be either 0 or 1, while in decimal system, each digit can be any of the 10 digits from 0 to 9.

- 2. Arithmetic operations: The basic arithmetic operations used in computer arithmetic are addition, subtraction, multiplication, and division. These operations are usually performed using arithmetic circuits within the CPU.

- 3. Overflow: In computer arithmetic, overflow occurs when the result of an arithmetic operation is too large to be represented in the available number of bits. This can result in incorrect or unexpected results.

- 4. Floating-point arithmetic: Floating-point arithmetic is used to represent and perform operations on non-integer numbers. It involves representing a number as a combination of a mantissa (or significand) and an exponent.

- 5. Round-off errors: Round-off errors occur in floating-point arithmetic due to the limited precision of the number representation. This can result in small inaccuracies in the computed results.

- 6. Bitwise operations: Bitwise operations are used to manipulate individual bits in a number. The basic bitwise operations include AND, OR, XOR, and NOT.

- 7. Two's complement representation: Two's complement representation is a method of representing negative numbers in binary. In this representation, the most significant bit is used as a sign bit, with 0 indicating a positive number and 1 indicating a negative number.

Overall, computer arithmetic is a fundamental aspect of computer science and is used in a wide range of applications, including scientific computing, financial analysis, and digital signal processing.

## 2.0 OBJECTIVES

At the end of this unit, you should be able to Recognize and explain the importance of various bases in computing. Perform arithmetic operations with floating-point numbers. Describe the fixed-point number representation and its applications.

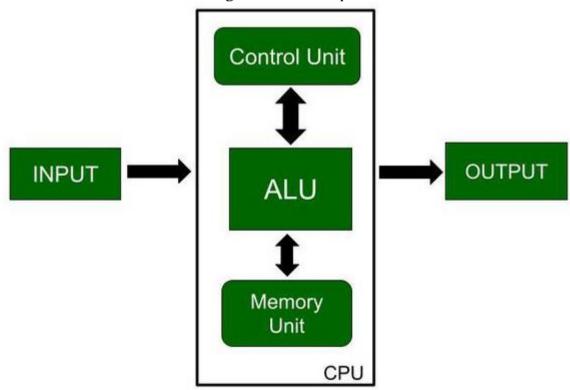

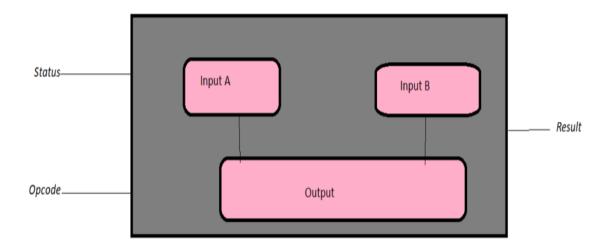

## 3.1 THE ARITHMETIC AND LOGIC UNIT

The arithmetic and logic unit (ALU) is that part of the computer that performs arithmetic and logical operations on data. All of the other elements of the computer system- Control unit, registers memory, I/0- are there mainly to bring into the ALU for it to process and then take the result back out.

An ALU and all electronic components in the computers are based on the use of simple digital logic devices that can store binary digits and perform simple Boolean logic operations. Data are presented to the ALU in registers and the results of an operation are stored in registers. These registers are temporary storage locations within the processor that are connected by signal paths to the ALU. The ALU may also set flags as the result of an operation. For example, an overflow flag is set to 1 if the result of a computation exceeds the length of the register into which it is to be stored. The flag values are also stored in registers within the processor. The control unit provides signals that control the operation of the ALU and the movement of the data into and out of the ALU.

Representing and storing numbers were the basic operations of the computers of earlier times. The real go came when computation, manipulating numbers like adding and multiplying came into the picture. These operations are handled by the computer's **arithmetic logic unit**

(ALU). The ALU is the mathematical brain of a computer. The first ALU (Arithmetic Logic Unit) was indeed the INTEL 74181, which was implemented as part of the 7400 series TTL (Transistor-Transistor Logic) integrated circuits. It was released by Intel in 1970.

ALU is a digital circuit that provides arithmetic and logic operations. It is the fundamental building block of the central processing unit of a computer. A modern central processing unit(CPU) has a very powerful ALU and it is complex in design. In addition to ALU modern CPU contains a control unit and a set of registers. Most of the operations are performed by one or more ALUs, which load data from the input register. Registers are a small amount of storage available to the CPU. These registers can be accessed very fast. The control unit tells ALU what operation perform the available data. to on calculation/manipulation, the ALU stores the output in an output register.

## 3.2 INTEGER REPRESENTATION

In the binary number, arbitrary numbers can be represented with just the digits zero and the minis sign, and the period or radix point.

$$-1101.0101_2 = -13.3125_{10}$$

For purposes of computer storage and processing, however, we do not have the benefits of minus signs and periods. Only binary digits (0 and 1) may be used

to represent numbers. If we are limited to non-negative integers, the representation is straight forward.

An 8-bit word can represent the numbers from 0 to 255, including

00000000 = 0 00000001 = 1 00101001 = 41 10000000 = 12811111111 = 255

In general, if an n-bit sequence of binary digits is interpreted as an unsigned integer, A it value is

$$A = n - 1$$

$$2 = 0$$

In going from the first to the second equation, we require that the least significant n - 1 bits do not change between the two representations. Then we get to next to the last equation, which is only true if all of the bits in positions theorem 2 are 1. Therefore, the sign-extension rule works.

Self-Assessment Exercises 1

Answer the following questions by choosing the most suitable option:

1. What is the range of numbers that can be represented using 8-bit

unsigned binary?

- A. 0 to 127

- B. -128 to 127

- C. 0 to 255

- D. -255 to 255

- 2. In two's complement representation, what does the most significant bit represent?

- A. The magnitude of the number

- B. The sign of the number

- C. The decimal point location

- D. The base of the number system

- 3. What is the primary advantage of two's complement representation?

- A. It uses less memory

- B. It simplifies arithmetic operations

- C. It allows larger numbers

- D. It is easier to understand

## **Fixed-point representation**

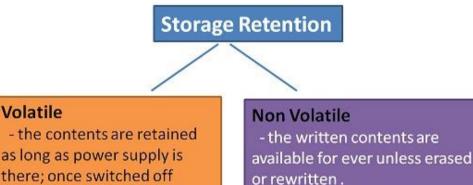

Finally, we mention that the representations discussed in this section are sometimes referred to as fixed points. This is because the radix point (binary point) is fixed and assumed to be to the right of the rightmost digit. The programmer can use the representation for binary fractions by scaling the numbers so that the binary poor implicitly positioned at some other location.

## **Negative Number Representation**

Sign Magnitude

Sign magnitude is a very simple representation of negative numbers. In sign-magnitude, the first bit is dedicated to representing the sign and hence it is called the sign bit.

The sign bit '1' represents a negative sign.

The sign bit '0' represents a positive sign.

In the sign-magnitude representation of n-bit number, the first bit will represent the sign, and the rest n-1 bits represent the magnitude of the number.

For example,

+25 = 011001

Where 11001 = 25

And 0 for '+'

-25 = 111001

Where 11001 = 25

And 1 for '-'.

# Range of number represented by sign magnitude method = -(2n-1-1)

to +(2n-1-1) (for n bit number)

But there is one problem in sign-magnitude and that is we have two

representations of 0 + 0 = 000000 - 0 = 100000

## 2's complement method

To represent a negative number in this form, first we need to take the 1's complement of the number represented in simple positive binary form and then add 1 to it.

For example:

(-8)10 = (1000)2

1's complement of 1000 = 0111

Adding 1 to it, 0111 + 1 = 1000

So,  $(-8)^{10} = (1000)^2$

Please don't get confused with  $(8)^{10} = 1000$  and  $(-8)^{10} = 1000$  as with 4 bits, we can't represent a positive number more than 7. So, 1000 is representing -8 only.

Range of number represented by 2's complement =  $(-2^{n-1} \text{ to } 2^{n-1} - 1)$

## Floating point representation of numbers

32-bit representation floating point numbers IEEE standard

## **Normalization**

- Floating point numbers are usually normalized

- The exponent is adjusted so that the leading bit (MSB) of the mantissa is 1

- Since it is always 1 there is no need to store it

- Scientific notation where numbers are normalized to give a single digit before the decimal point like in a decimal system e.g.  $3.123 \times 10^3$  Some insight into two complement addition and subtraction can be gained by looking at a geometric depiction. The circle in the upper half of each part of the figure is formed by selecting the appropriate segment of the number line and joining the endpoints. Note that when the numbers are laid out on a circle, the twos complement of any number are horizontally opposite that number (indicated by dashed horizontal lines). Starting at any number on the circle, we can add positive k (or subtract negative k), to that number by moving k positions clockwise, and we can subtract positive k (of add negative k) from that number by moving k positions counterclockwise. If an arithmetic operation results in traversal of the point where the endpoints are joined, an incorrect answer is given (overflow).

The central element is a binary adder, which presents two numbers for addition and produces a sum and an overflow indication. The binary adder treats the two numbers as unsigned integers. In addition, the two numbers are presented to the adder from two registers, designated in this case as A and B registers. The result may be stored in one of these registers or a third. The overflow indication is stored in a 1-bit overflow flag (0 = no) overflow; I = voerflow. For subtraction, the

## 4.0 CONCLUSION

Numbers are represented in binary form and the algorithms used for basic

arithmetic operators are add, subtract, multiply, and divide

#### 5.0 SUMMARY

- An ALU and all electronic components in the digital logic devices that store binary digits and perform simple Boolean logic operations

- Overflow rule occurs when two numbers positive or negative numbers are added and the result of the addition has the opposite sign.

- Subtraction flow is to subtract one number (subtracted) from another (minuend) take the two compliments (negation) of the subtrahend and hold it to the minuend.

Floating point numbers are expressed as a number (significant) multiplied by a constant (base) raised to some integer power (exponent). It can be used to represent very large and very small numbers.

## 7.1 Possible Answers to Self-Assessment Exercises

Self-Assessment Exercise 1

- 1. C

- 2. B

- 3. B

#### 6.0 TUTOR- MARKED ASSIGNMENT

- 1. What is a sign-extension rule for two compliment numbers?

- 2. Find the following differences using two complement arithmetic:

- a. 1111011 b. 10101110 c. 111110010111

- -100100 -111-1-1 -111010010101

## 7.0 Reference and further reading

Null, L. (2023). Essentials of Computer Organization and Architecture. Jones & Bartlett Learning.

Englander, I., & Wong, W. (2021). The architecture of computer hardware, systems software, and networking: An information technology approach. John Wiley & Sons.

Swartzlander, E. editor computer Arithmetic, volumes I and II. Los Alamitiss, CA IEEE Computer society press, 1990.

## UNIT 2 CONTROL FLOW DESIGN/OPERATION

- 1.0 Introduction

- 2.0 Objectives

- 3.0 Main Content

- 3.1 Micro- Operation

- 3.2 Control of the Processor

- 3.3 Hard-wired implementation

- 3.4 Micro-programmed control

- 4.0 Conclusion

- 5.0 Summary

- 6.0 T. M.A

- 7.0 Reference and further reading

#### 1.0 Introduction

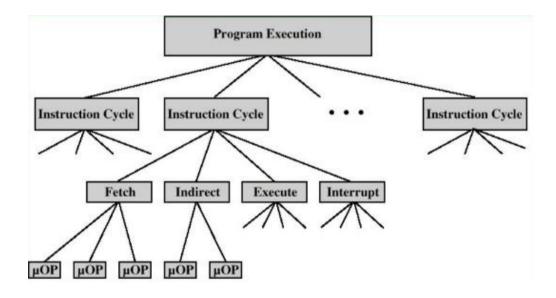

The execution of an instruction involves the execution of a sequence of sub-steps, generally called cycles. For example, an execution may consist of fetch, indirect, execute, and interrupt cycles. Each cycle is in turn made up is a sequence of more fundamental operations called micro-operations. A single micro-operation generally involves transfer between registers a register and an external bus, or a simple ALU operation.

## 2.0 At the end of this unit, you should be able to

- Understand that each cycle is in turn made up of a sequence of more fundamental operations called micro-operations.

- Identify hardwired implementation

- Explain micro-programmed control

## 3.1 MICRO OPERATIONS

The prefix micro refers to the fact that each step is very simple and accomplishes very little. To design a control unit each of the smaller cycles involves a series of steps each of which involves the processor registers. We refer to these steps as micro-operations. Micro operations are the functional, or atomic operations of a processor.

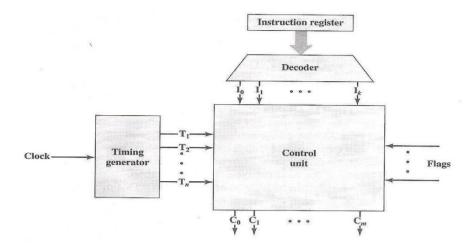

Three. Now, we turn to the question of how these functions are performed or, more specifically, how the various elements of the processor are controlled to provide these functions. Thus, we turn to a discussion of the control unit, which controls the operation of the processor.

We have seen that the operation of a computer, in executing a program, consists of a sequence of instruction cycles, with one machine instruction per cycle. Of course, we must remember that this sequence of instruction cycles is not necessarily the same as the *written sequence* of instructions that make up the program, because of the existence of branching instructions. What we are referring to here is the execution *time sequence* of instructions.

We have further seen that each instruction cycle is made up of several smaller units. One subdivision that we found convenient is fetch, indirect,

execute, and interrupt, with only fetch and execute cycles always occurring.

To design a control unit, however, we need to break down the description further. In our discussion of pipelining in Chapter 12, we began to see that further decomposition is possible. We will see that each of the smaller cycles involves

a series of steps, each of which involves the processor registers. We will refer to these steps as micro-operations. The prefix *micro* refers to the fact that each step is very simple and accomplishes very little. Figure 15.1 depicts the relationship among the various concepts we have been discussing. To summarize, the execution of a program consists of the sequential execution of instructions. Each instruction is executed during an instruction cycle made up of shorter subcycles (e.g., fetch, indirect, execute, interrupt). The execution of each subcycle involves one or more shorter operations, that is, micro- operations.

Micro-operations are the functional, or atomic, operations of a processor. In this section, we will examine micro-operations to gain an understanding of how the events of any instruction cycle can be described as a sequence of such m' operations. A simple example will be used. In the remainder of this chapter.

-then show how the concept of micro-operations serves as a guide to the design control unit. Figure 7 displayed the contituent element of a program execution.

Figure 7. Contituent element of a program execution

'We begin by looking at the fetch cycle, which occurs at the beginning of each instruction cycle and causes an instruction to be fetched from memory.

Memory address register (MAR): Is connected to the address lines of the bus. It specifies the address in memory for a read or write operation.

Memory buffer register (MBR): Is connected to the data lines of the system --

\_ It contains the value to be stored in memory or the last value read from melr

\_ Program counter (PC): Holds the address of the next instruction to be fetched

Instruction register (IR): Holds the last instruction fetched.

Let us look at the sequence of events for the fetch cycle from the point of view of its effect on the processor registers. An example appears in Figure 5 at the beginning of the fetch cycle, the address of the next instruction to be executed is in the program counter (PC); in this case, the address is 1100100. The first steto move that addresses to the memory address register

(MAR) because this is only registered and connected to the address lines of the system bus. The second step bring in the instruction. The desired address (in the MAR) is placed on the adder. We have seen that the operation of a computer, in executing a program, consists of a sequence of instruction cycles, with one machine instruction per cycle. Of course, we must remember that this sequence of instruction cycles is not necessarily the same as the *written sequence* of instructions that make up the program, because of the existence of branching instructions. What we are referring to here is the execution *time sequence* of instructions.

We have further seen that each instruction cycle is made up of several smaller units. One subdivision that we found convenient is fetch, indirect, execute, and interrupt, with only fetch and execute cycles always occurring.

To design a control unit, however, we need to break down the description further. We will see that each of the smaller cycles involves a series of steps, each of which involves the processor registers. We will refer to these steps as micro-operations. The prefix *micro* refers to the fact that each step is very simple and accomplishes very little. Figure 15.1 depicts the relationship among the various concepts we have been discussing. To summarize, the execution of a program consists of the sequential execution of instructions. Each instruction is executed during an instruction cycle made up of shorter subcycles (e.g., fetch, indirect, execute, interrupt). The execution of each subcycle involves one or more shorter operations, that is, micro-operations.

Micro-operations are the functional, or atomic, operations of a processor. bus, the control unit issues a READ command on the control bus, and the result appears on the data bus and is copied into the memory buffer register (MBR). We also need to increment the PC by the instruction length to get ready for the next instruction. Because these two actions (read word from memory, increment PC) do not interfere with each other, we can do them simultaneously to save time. The third step is to move the contents of the MBR to the instruction register (IR). This frees up the MBR for use during a possible indirect cycle.

Thus, the simple fetch cycle consists of three steps and four microoperations. Each micro-operation involves the movement of data into or out of a register. So long as these movements do not interfere with one another, several of them can take place during one step, saving time. Symbolically, we can write this sequence of events as follows:

$t_1$ : MAR E- (PC) t2: MBR <-- Memory PC <- (PC) + I t3: IR <-- (MBR) where I is the instruction length. We need to make several comments about this sequence. We assume that a clock is available for timing purposes and that it emits regularly spaced clock pulses. Each clock pulse defines a time unit. Thus, all time units are of equal duration. Each microoperation can be performed within the time of a single time unit. The notation ( $t_i$ ,  $t_2$ ,  $t_3$ ) represents successive time units. In words, we have I First-time unit: Move contents of PC to MAR.

Second-time unit: Move contents of the memory location specified by MAR to MBR. Increment by I the contents of the PC.

Third-time unit: Move contents of MBR to IR.

Note that the second and third micro-operations both take place during the second time unit. The third micro-operation could have been grouped with the fourth without affecting the fetch operation:

$t_1$ : MAR <- (PC)  $t_2$ : MBR <- Memory t3: PC E- (PC) + I IR <- (MBR) The groupings of micro-operations must follow two simple rules:

The proper sequence of events must be followed. Thus (MAR <u>-</u> (PC)) must precede (MBR - Memory) because the memory read operation makes use of the address in the MAR.

Conflicts must be avoided. One should not attempt to read to and write from the same register in a one-time unit, because the results would be unpredictable. For example, the micro-operations (MBR  $\phi$ -- Memory) and (IR <- MBR) should not occur during the same time unit.

A final point worth noting is that one of the micro-operations involves an addition. To avoid duplication of circuitry, this addition could be performed by the ALU. The use of the ALU may involve additional micro-operations, depending on the functionality of the ALU and the organization of the processor. Whereas micro-operations are ignored in that figure, this discussion shows the micro-operations needed to perform the sub-cycles of the instruction cycle.

Once an instruction is fetched, the next step is to fetch source operands. Continuing our simple example, let us assume a one-address instruction format, with direct and indirect addressing allowed. If the instruction specifies an indirect address, then an indirect cycle must precede the execute cycle.

```

t_1: MAR < -(IR(Address))

t_2: MBR F - Memory

t_3: IR(Address) F - (MBR(Address))

```

The address field of the instruction is transferred to the MAR. This is then used to fetch the address of the operand. Finally, the address field of the IR is updated from the MBR, so that it now contains a direct rather than

an indirect address.

The IR is now in the same state as if indirect addressing had not been used and it is ready for the execution cycle. We skip that cycle for a moment, to consider t interrupt cycle.

After the execute cycle, a test is made to determine whether any:-\_abled interrupts have occurred. If so, the interrupt cycle occurs. The nature of the cycle varies greatly from one machine to another. We present a very simple sequeof events, as illustrated in Figure 12.8. We have

t<sub>1</sub>: MBR E- (PC)

t<sub>2</sub>: MAR F- Save Address PC F- Routine Address

t<sub>3</sub>: Memory E- (MBR)

In the first step, the contents of the PC are transferred to the MBR, so that u- can be saved for return from the interrupt. Then the MAR is loaded with the add- at which the contents of the PC are to be saved, and the PC is loaded with the add to the MAR and PC, respectively. In any case, once this is done, the final step is to store the MBR, which contains the old value of the PC, in memory. The processor is now ready to begin the next instruction cycle.

The fetch, indirect, and interrupt cycles are simple and predictable. Each involves a small, fixed sequence of micro-operations and, in each case, the same micro-operations are repeated each time around.

This is not true of the execution cycle. Because of the variety of opcodes, there are several different sequences of micro-operations that can occur. Let us consider several hypothetical examples.

First, consider an add instruction:

ADD R1, X

which adds the contents of location X to register R1. The following sequence of micro-operations might occur:

We begin with the IR containing the ADD instruction. In the first step, the address portion of the IR is loaded into the MAR. Then the referenced memory

location is read. Finally, the contents of RI and MBR are added by the ALLT.

Again. This is a simplified example. Additional micro-operations may be required to extract the register reference from the IR and perhaps to stage the ALt inputs or outputs in some intermediate registers.

Let us look at two more complex examples. A common instruction is increment and skip if zero:

The content of location X is incremented by l. If the result is 0, the next instruction is skipped. A possible sequence of micro-operations is

ti: MAR <-- (IR(address)) t2: MBR- F- Memory

tz: MBR < -- (MBR) + 1

tu: Memory <- (MBR)

If ((MBR) = 0) then (PC F - (PC) + I)

The new feature introduced here is the conditional action. The PC is incremented if (MBR) = 0. This test and action can be implemented as

one micro-operation. Note also that this micro-operation can be performed during the same time unit during which the updated value in MBR is stored back in memory.

It is worth pondering the minimal nature of the control unit. The control unit is the engine that runs the entire computer. It does this based only on knowing the instructions to be executed and the nature of the results of arithmetic and logical operations (e.g., positive, overflow, etc.). It never gets to see the data being processed or the actual results produced. It controls everything with a few control signals to points within the processor and a few control signals to the system bus.

Self-Assessment Exercises 1

| Fill in the gaps in the sentences below with the most suitable words:                              |

|----------------------------------------------------------------------------------------------------|

| 1 are the functional, or atomic, operations of a processor.                                        |

| 2. The fetch cycle consists of steps and micro-operations.                                         |

| 3. A control unit uses fixed logic circuits while a control unit stores control signals in memory. |

## INTERNAL PROCESSOR ORGANIZATION

Figure 8 indicates the use of a variety of data paths. The complexity of this type of organization should be clear. Using an internal processor bus, Figure 8 can be rearranged. A single internal bus connects the ALU and all processor registers.

CPU with Internal Bus.

Figure 8. CPU with internal bus

Gates and control signals are provided for the movement of data onto and off the bus from each register. Additional control signals control data transfer to and from the system (external) bus and the operation of the ALU.

Two new registers, labeled Y and Z, have been added to the organization. These are needed for the proper operation of the ALU. When an operation involving two operands is performed, one can be obtained from the internal bus, but the other must be obtained from another source. The AC could be used for this purpose, but this limits the flexibility of the system and would not work with a processor with multiple general-purpose registers. Register Y provides temporary storage for the other input. The ALU is a combinatorial circuit with no internal storage. Thus, when control signals activate an ALU function, the input to the ALU is transformed into the output. Thus, the output of the ALU cannot be directly connected to the bus, because this output would feed back to the input. Register Z provides temporary output storage. With this arrangement, an operation to add a value from memory to the AC would

have the following steps:

t<sub>1</sub>: MAR <- (IR(address))

t<sub>2</sub>: MBR E- Memory

$t_3$ : Y <-(MBR)

t4: Z f- (AC) + (Y)

$t_s$ : AC F- (Z)

Other organizations are possible, but, in general, some sort of internal bus or set of internal buses is used. The use of common data paths simplifies the interconnection layout and the control of the processor. Another practical reason for the use of an internal bus is to save space.

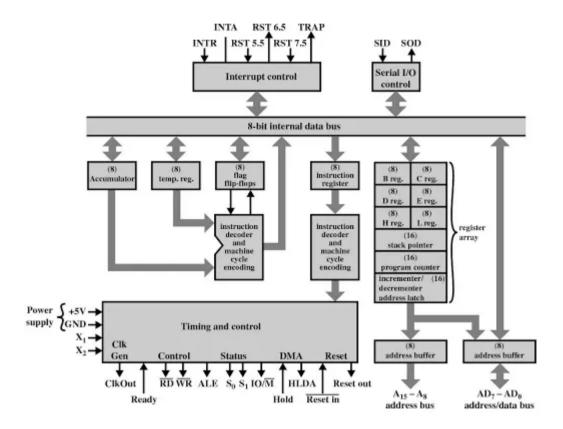

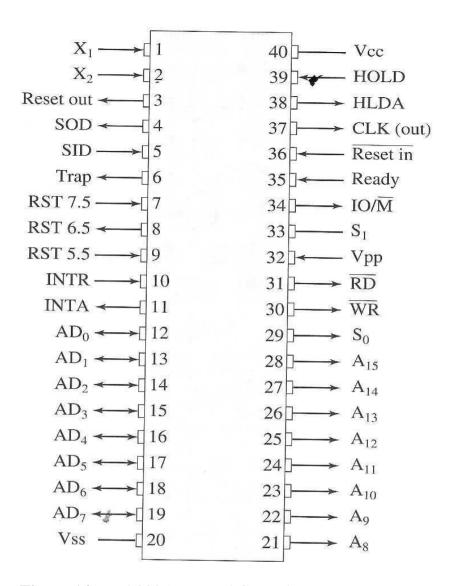

To illustrate some of the concepts introduced thus far in this chapter, let us consider the Intel 8085. Its organization is shown in Figure 9. Several key components that may not be self-explanatory are:

**Incrementer/decrementer address latch:** Logic that can add 1 to or subtract 1 from the contents of the stack pointer or program counter. This saves time by avoiding the use of the ALU for this purpose.

**Interrupt control:** This module handles multiple levels of interrupt signals.

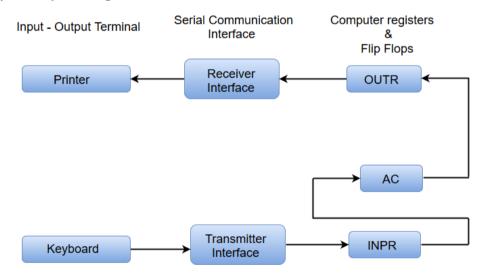

**Serial I/O control:** This module interfaces to devices that communicate 1 bit at a time. These signals are the interface between the 8085 processor and the rest of the system (Figure 10).

Figure 9. Intel 8085 CPU Block Diagram

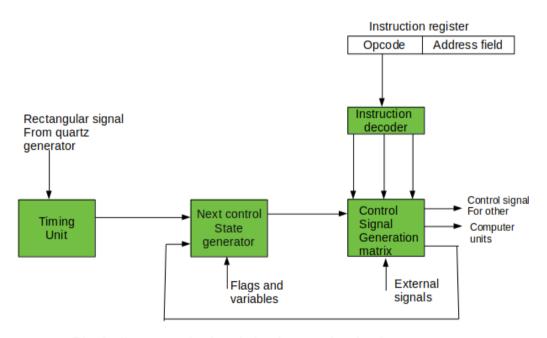

The control unit is identified as having two components labeled (1) in decoder and machine cycle encoding and (2) in timing and control. The timing of processor operations is synchronized by the clock trolled by the control unit with control signals. Each instruction cycle i, into from one to five *machine cycles*; each machine cycle is in turn diN from three to five states. Each state lasts one clock cycle. During a state. The son performs one or a set of simultaneous micro-operations as determined control signals.

The number of machine cycles is fixed for a given instruction but one instruction to another. Machine cycles are defined to be equivalent cesses. Thus, the number of machine cycles for an instruction depends on a bar of times the processor must communicate with external devices. For e an instruction consists of two 8-bit portions, and then two machine, cycles fetch the instruction. If that instruction involves a 1-byte memory or 1/0 then a third machine cycle is required for execution.

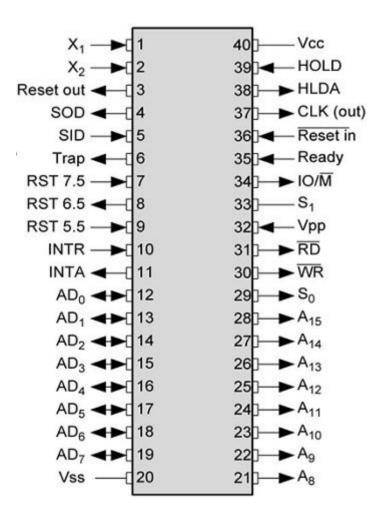

Figure 10. Inter 8085 pin configuration

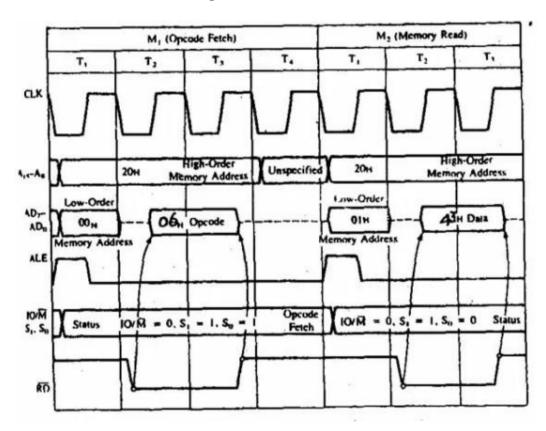

Figure 11 gives an example of 8085 timing, showing the value of external control signals. Of course, at the same time, the control unit generates

internal control signals that control internal data transfers. The diagram shows the instruction cycle for an OUT instruction. Three machine cycles (Ml, M2, M3) are needed. During the first, the OUT instruction is fetched. The second machine cycle fetches the second half of the instruction, which contains the number of the 1/O device selected for output. During the third cycle, the contents of the AC are written out to the selected device over the data bus.

The Address Latch Enabled (ALE) pulse signals the start of each machine cycle from the control unit. The ALE pulse alerts external circuits. During timing state  $T_1$  of machine cycle  $M_r$ , the control unit sets the IO/M signal to indicate that this is a memory operation. Also, the control unit causes the contents of the PC to be placed on the

Figure 11. The timing diagram for inter 8085 out instruction

The timing diagram for inter 8085 out instruction addressed memory

module places the contents of the addressed memory vocation on the

module places the contents of the addressed memory vocation on the address/data bus. The control unit sets the Read Control (RD) signal to indicate a read, but it waits until  $T_3$  to copy the data from the bus. This gives the memory module time to put the data on the bus and for the signal levels to stabilize. The final state,  $T_4$ , is a bus *idle* state during which the processor decodes the instruction. The remaining machine cycles proceed similarly.

Finally, consider a subroutine call instruction. As an example, consider a branch and-save-address instruction:

#### BSA X

The address of the instruction that follows the BSA instruction is saved in location X, and execution continues at location X + I. The saved address will later be used for return. This is a straightforward technique for providing subroutine calls. The following micro-operations suffice:

t,: MAR E- (IR(address)) MBR ~ (PC)

t<sub>z</sub>: PC <-- (IR(address)) Memory <-- MBR)

$t_3: PC <- (PC) + I$

The address in the PC at the start of the instruction is the address of the next instruction in sequence. This is saved at the address designated in the IR. The later address is also incremented to provide the address of the instruction for the next - instruction cycle.

We have seen that each phase of the instruction cycle can be decomposed into a sequence of elementary micro-operations. In our example, there is one sequence eac= for the fetch, indirect, and interrupt cycles, and, for the execute cycle, there is one sequence of micro-operations for each opcode. To complete the picture, we need to tie sequences of micro-operations together, and this is done in Figure 15.3. We assume a new 2-bit register called the *instruction cycle code (ICC)*. The ICC designates the state of the processor in terms of which portion of the cycle it is in:

00: Fetch 01: Indirect

10: Execute 11:

# **Interrupt**

At the end of each of the four cycles, the ICC is set appropriately. The indirect cycle is always followed by the execute cycle. The interrupt cycle is always followed by the fetch cycle. For both the fetch and execute cycles, the next cycle depends on the state of the system.

Of course, this is a simplified example. The flowchart for an actual processor would be more complex. In any case, we have reached the point in our discussion in which the operation of the processor is defined as the performance of a sequence of micro-operations. We can now consider how the control unit causes this sequence to occur of tbp r of the interrupt-processing routine. These two actions may each be single micro-operation. However, because most processors provide multiple tyr and/or levels of interrupts, it may take one or more additional micro-operations to obtain the Save Address and the Routine Address before they can be transfer the events of any instruction cycle can be described as a sequence of such micro operations. A simple example will be used. In the remainder of this chapter, we then show how the concept of micro- operations serves as a guide to the design of the control unit.

# THE FETCH CYCLE

We begin by looking at the fetch cycle, which occurs at the beginning of each instruction cycle and causes an instruction to be fetched from memory. Four registers are involved:

• Memory address register (MAR): Is connected to the address lines of the system bus. It specifies the address in memory for a read or

write operation.

- **Memory buffer register (MBR):** Is connected to the data lines of the system bus. It contains the value to be stored in memory or the last value read from memory.

- **Program counter (PC):** Holds the address of the next instruction to be fetched.

- **Instruction register (IR):** Holds the last instruction fetched.

Let us look at the sequence of events for the fetch cycle from the point of view of its effect on the processor registers. At the beginning of the fetch cycle, the address of the next instruction to be executed is in the program counter (PC); in this case, the address is 1100100. The first step is to move that address to the memory address register (MAR) because this is the only register connected to the address lines of the system bus. The second step is to bring in the instruction. The desired address (in the MAR) is placed on the bus, the control unit issues a READ command on the control bus, and the result appears on the data bus and is copied into the memory buffer register (MBR). We also need to increment the PC by the instruction length to get ready for the next instruction. Because these two actions (read word from memory, increment PC) do not interfere with each other, we can do them simultaneously to save time. The third step is to move the contents of the MBR to the instruction register (IR). This frees up the MBR for use during a possible indirect cycle.

Thus, the simple fetch cycle consists of three steps and four microoperations. Each micro-operation involves the movement of data into or out of a register. So long as these movements do not interfere with one another, several of them can take place during one step, saving time. Symbolically, we can write this sequence of events as follows:

where I is the instruction length. We need to make several comments about this sequence. We assume that a clock is available for timing purposes and that it emits regularly spaced clock pulses. Each clock pulse defines a time unit. Thus, all time units are of equal duration. Each microoperation can be performed within the time of a single time unit. The notation (t1, t2, t3) represents successive time units. In words, we have First-time unit: Move contents of PC to MAR.

- **Second-time unit:** Move contents of the memory location specified by MAR to MBR. Increment by I the contents of the PC.

- Third-time unit: Move contents of MBR to IR.

Note that the second and third micro-operations both take place during the second time unit. The third micro-operation could have been grouped with the fourth without affecting the fetch operation:

The groupings of micro-operations must follow two simple rules:

The proper sequence of events must be followed. Thus (MAR <u>-</u> (PC)) must precede (MBR - Memory) because the memory read operation makes use of the address in the MAR. Conflicts must be avoided. One should not attempt to read to and write from the same register in a one-time unit, because the results would be unpredictable. For example, the

micro-operations (MBR Memory) and (IR <u>E-</u> MBR) should not occur during the same time unit.

A final point worth noting is that one of the micro-operations involves an addition. To avoid duplication of circuitry, this addition could be performed by the ALU. The use of the ALU may involve additional micro-operations, depending on the functionality of the ALU and the organization of the processor.

Whereas micro-operations are ignored in that figure, this discussion shows the micro-operations needed to perform the subcycles of the instruction cycle.

Once an instruction is fetched, the next step is to fetch source operands. Continuing our simple example, let us assume a one-address instruction format, with direct and indirect addressing allowed. If the instruction specifies an indirect address, then an indirect cycle must precede the execute cycle.

The address field of the instruction is transferred to the MAR. This is then used to fetch the address of the operand. Finally, the address field of the IR is updated from the MBR, so that it now contains a direct rather than an indirect address.

The IR is now in the same state as if indirect addressing had not been used, and it is ready for the execute cycle. We skip that cycle for a moment, to consider the interrupt cycle.

After the execute cycle, a test is made to determine whether any enabled interrupts have occurred. If so, the interrupt cycle occurs. The nature of this cycle varies greatly from one machine to another. We have

t<sub>1</sub>: MBR <-- (PC)

t<sub>2</sub>: MAR <-- Save Address PC <-- Routine ddress

t<sub>3</sub>: Memory <-- (MBR)

In the first step, the contents of the PC are transferred to the MBR, so that they can be saved for return from the interrupt. Then the MAR is loaded with the address at which the contents of the PC are to be saved, and the PC is loaded with the address of the start of the interrupt-processing routine. These two actions may each be a single micro-operation. However, because most processors provide multiple types and/or levels of interrupts, it may take one or more additional micro- operations to obtain the Save Address and the Routine Address before they can be transferred to the MAR and PC, respectively. In any case, once this is done, the final step is to store the MBR, which contains the old value of the PC, in memory. The processor is now ready to begin the next instruction cycle.

The fetch, indirect, and interrupt cycles are simple and predictable. Each involves a small, fixed sequence of micro-operations and, in each case, the same micro-operations are repeated each time around.

This is not true of the execute cycle. Because of the variety of opcodes, there are various sequences of micro-operations that can occur. Let us consider several hypothetical examples.

First, consider an add instruction:

which adds the contents of location X to register R1. The following sequence of micro-operations might occur:

t<sub>1</sub>: MAR <-- (IR(address))

t<sub>2</sub>: MBR <-- Memory

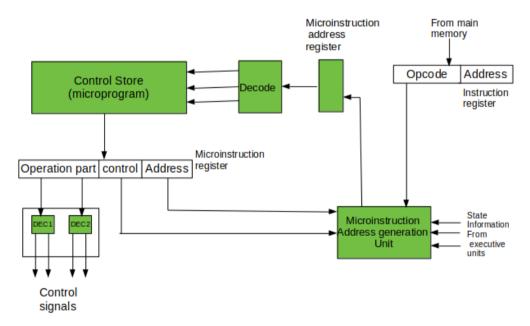

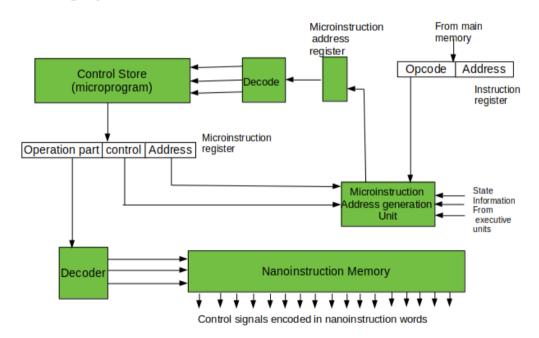

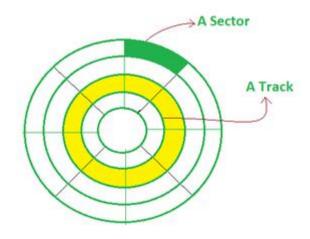

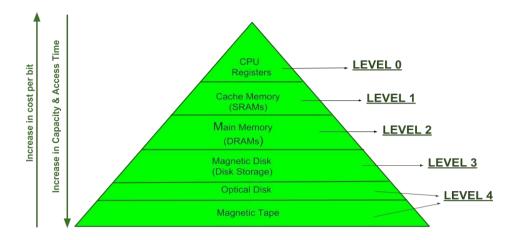

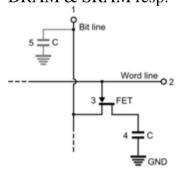

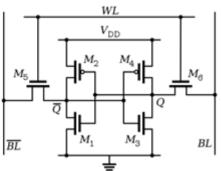

$t_3$ : R1 ~- (R1) + (MBR)